# Translation Validation for the LLVM Compiler

#### Kevin Jacobus de Vos

Thesis to obtain the Master of Science Degree in

## Computer Science and Engineering

Supervisors: Prof. Nuno Claudino Pereira Lopes Prof. José Carlos Alves Pereira Monteiro

#### **Examination Committee**

Chairperson: Prof. Luís Manuel Antunes Veiga Supervisor: Prof. Nuno Claudino Pereira Lopes

Member of the Committee: Prof. José Faustino Fragoso Femenin dos Santos

### ${\bf Acknowledgments}$

I would like to thank my advisors José Monteiro and Nuno Lopes for their great help and guidance as without them I would not have been able to finish this work. Their support helped me learn and understand complex concepts and build algorithms that made great progress towards achieving the goals of this work.

I would also like to thank my family and advisors for encouraging and supporting me during this time, especially when I felt like giving up and when I was not making any progress.

### Abstract

Compilers can have many bugs and miscompile, often resulting in unintended program behavior not specified by the original program. Translation validation is a technique that verifies the correctness of compilation given the source and target code. We extend Alive [1] to 1) reduce the SMT formula sizes generated to improve performance and 2) significantly increase analysis coverage with a new loop unrolling algorithm for loops written in Alive IR. Since the LLVM compiler is susceptible to miscompilation we do not use any loop unroll mechanisms available in LLVM. We evaluate our main contribution by measuring the increase of both block and path coverage for a large number of programs. We have been able to reduce Alive execution time with our SMT formula reduction algorithms and find multiple bugs in the LLVM compiler using our loop unrolling algorithm. Finding and fixing these bugs is essential to reducing the likelihood of miscompilation in LLVM.

**Keywords:** Compilers - Software verification - Translation validation - Loop unroll - Refinement - Undefined behavior

#### Resumo

Os compiladores podem ter bastantes erros e podem compilar incorretamente, muitas das vezes resultando em comportamento differente do especificado pelo programa original. Translation Validation é uma técnica capaz de verificar se as transformações aplicadas durante compilação são corretas. Estendemos o Alive [1] com o objetivo de 1) reduzir tamanhos das fórmulas SMT geradas e desta forma melhorar o desempenho do Alive, 2) aumentar substancialmente a cobertura de anàlise do Alive com um novo algorithmo de desenrolar ciclos para ciclos escritos em Alive IR. Dado que o compilador LLVM pode compilar programas incorretamente não utilizamos mecanismos de desenrolamento de ciclos disponíveis pelo LLVM. Avaliamos a nossa principal contribuição através da medida de cobertura de blocos e cobertura de caminhos para um grande número de programas. Foi possível reduzir o tempo de execução do Alive com os nossos algoritmos de redução de tamanho de fórmulas SMT e foi possível encontrar vários erros no compilador LLVM com o nosso algoritmo de desenrolamento de ciclos. Encontrar e resolver erros em compiladores como o compilador LLVM é essencial para reduzir a probabilidade de compilação incorreta.

**Keywords:** Compiladores - Verificação de software - Desenrolamento de loops - Refinação - Comportamento não definido

# Contents

|          | Ack  | nowledgments                                        | iii  |

|----------|------|-----------------------------------------------------|------|

|          | Abs  | cract                                               | iv   |

|          | Resi | ımo                                                 | v    |

|          | List | of Tables                                           | viii |

|          | List | of Figures                                          | ix   |

| 1        | Inti | oduction                                            | 2    |

|          | 1.1  | Thesis Overview                                     | 4    |

| <b>2</b> | Rel  | ated Work                                           | 6    |

|          | 2.1  | Compiler Verification and Translation Validation    | 6    |

|          | 2.2  | Program Representations                             | 9    |

|          |      | 2.2.1 Control Flow Graph                            | 10   |

|          |      | 2.2.2 Programs in LLVM IR                           | 10   |

|          |      | 2.2.3 Intermediate Representations                  | 10   |

|          | 2.3  | Program Analysis Techniques                         | 13   |

|          |      | 2.3.1 Model Checking                                | 13   |

|          |      | 2.3.2 Symbolic Execution                            | 14   |

|          |      | 2.3.3 Bounded Model Checking vs. Symbolic Execution | 16   |

|          | 2.4  | Undefined Behavior                                  | 17   |

|          | 2.5  | Summary                                             | 19   |

| 3        | Loo  | ps                                                  | 21   |

|          | 3.1  | Nested Loops                                        | 23   |

|          | 3.2  | Loop Identification                                 | 24   |

|          | 3.3  | Multiple Loops per Header                           | 25   |

|          | 3.4  | Loop Trees                                          | 25   |

|          | 3.5  | Loop Unrolling                                      | 26   |

|          |      | 3.5.1 Reducible Loops                               | 26   |

|          |      | 3.5.2 Loop Unroll Factor                            | 28   |

|          |      | 3.5.3 Algorithm                                     | 29   |

|          |      | 2.5.4 Instruction Detains                           | 91   |

| Bi | bliog | graphy                                                                                      | 66       |

|----|-------|---------------------------------------------------------------------------------------------|----------|

| 6  | Con   | aclusions and Future Work                                                                   | 65       |

|    | 5.4   | Reduction of Phi SMT Formulas                                                               | 63       |

|    | 5.3   | Reduction of UB SMT Formulas                                                                | 62       |

|    |       | $5.2.2  Loop Vectorize/pr 30654-phiscev-sext-trunc.ll \ . \ . \ . \ . \ . \ . \ . \ . \ . $ | 61       |

|    |       | 5.2.1 LoopReroll/basic.ll                                                                   | 61       |

|    | 5.2   | Bugs Found in LLVM                                                                          | 61       |

|    | 5.1   | Loop Unrolling                                                                              | 57       |

| 5  | Res   | ults                                                                                        | 57       |

|    | 4.13  | Summary                                                                                     | 56       |

|    |       | Reduction of Phi SMT Formulas                                                               | 53       |

|    |       | UBReduction with Heuristics                                                                 | 52<br>52 |

|    |       | UBReduction with Conditional Post-dominators                                                | 51       |

|    | 4.9   | UBReduction with Post-dominators                                                            | 49       |

|    | 4.0   | 4.8.4 Dead Vertex Removal                                                                   | 48       |

|    |       | 4.8.3 Dominator Trees                                                                       | 48       |

|    |       | 4.8.2 Post-dominance                                                                        | 47       |

|    |       | 4.8.1 Dominance                                                                             | 47       |

|    | 4.8   | Dominators and Post-dominators                                                              | 47       |

|    | 4.7   | Formula Size Explosion                                                                      | 46       |

|    | 4.6   | Rewriting Expressions in Z3                                                                 | 46       |

|    | 4.5   | Basic UB Reduction Algorithm                                                                | 44       |

|    | 4.4   | Challenges with Building ite Expressions                                                    | 43       |

|    | 4.3   | SMT Expression Sharing and Redundancy                                                       | 42       |

|    | 4.2   | Motivation for ite Expressions                                                              | 42       |

|    | 4.1   | Current SMT Formulas in Alive                                                               | 41       |

| 4  |       | Γ Formula Reduction                                                                         | 41       |

|    | 3.6   | Summary                                                                                     | 39       |

|    | 9 6   | 3.5.6 Irreducible Loops and Node Splitting                                                  | 38       |

|    |       |                                                                                             |          |

|    |       | 3.5.5 Optimality of Loop Unroll                                                             | 37       |

# List of Tables

| 5.1 | Average number of paths covered (Paths) over all functions in LoopVectorize and LoopUnroll;   |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | total number of times Alive reports transformations with false preconditions (Pre); the       |    |

|     | total number of timeouts (Timeo.) with loop unroll factors $0,16,32$ with $0$ corresponding   |    |

|     | to no loop unroll                                                                             | 60 |

| 5.2 | Average number of paths covered (Paths) over all functions in each benchmark, total number    |    |

|     | of times Alive reports transformations with false preconditions (Pre); the total number of    |    |

|     | timeouts (Timeo.) for four different benchmarks with loop unroll factors $0,1,2,4$ and $8,$   |    |

|     | where 0 corresponds to no loop unroll                                                         | 60 |

| 5.3 | Execution times for the four versions and the three different benchmarks measured in          |    |

|     | seconds (s)                                                                                   | 63 |

| 5.4 | Memory usage for created formulas for four versions and three different benchmarks            |    |

|     | measured in megabytes (MB)                                                                    | 63 |

| 5.5 | Execution times for the current version of Alive $v_0$ , and PhiReduction $v_1$ for reduction |    |

|     | of phi formula sizes. The versions of LLVM, Z3 and Alive used are the same as those in        |    |

|     | Section 5.3.                                                                                  | 63 |

# List of Figures

| 1.1  | Incorrect transformation showcasing the subtleties of compiler math                                                 | 2  |

|------|---------------------------------------------------------------------------------------------------------------------|----|

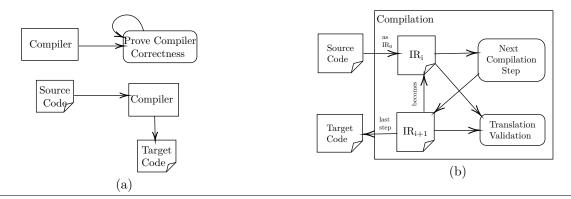

| 1.2  | (a) Compiler Verification: The compiler is verified prior to compilation. (b) Translation                           |    |

|      | Validation when performed at each step of compilation: during compilation, the source                               |    |

|      | code is transformed to an intermediate representation (IR) at each compiler step. Then the                          |    |

|      | previous $\mathrm{IR}_i$ and the new $\mathrm{IR}_{i+1}$ are fed into the translation validator                     | 3  |

| 1.3  | Simple program with a while loop written in C                                                                       | 4  |

| 2.1  | An example of a transformation with the source code in (a) and the target code in (b)                               | 7  |

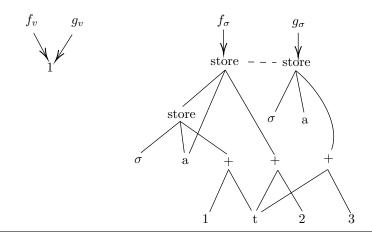

| 2.2  | Combined Program Expression Graph (PEG). The dashed lines represent the equality                                    |    |

|      | relations generated in the equality saturation technique between graph vertices, and in                             |    |

|      | this case, both $f_{\sigma}$ and $g_{\sigma}$ , representing the heap resulting of executing a function $f$ and $g$ |    |

|      | respectively, are equivalent.                                                                                       | 7  |

| 2.3  | A loop fusion optimization example. Source code on the left (a) and target on the right (b).                        | 9  |

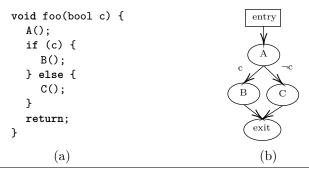

| 2.4  | A control flow graph (b) for the example program (a)                                                                | 10 |

| 2.5  | Example illustrating the differences between code not SSA form on the left and the code in                          |    |

|      | SSA form on the right                                                                                               | 10 |

| 2.6  | A code fragment in SSI form where the variables $y_2$ and $y_3$ are associated with the branch                      |    |

|      | predicate $y_0 < 0$ through the $\pi$ -function                                                                     | 11 |

| 2.7  | Code example not written in Gated SSA in (a), the same example but written in Gated                                 |    |

|      | SSA form in (b), and a shared value graph of this example in (c). $\dots$                                           | 12 |

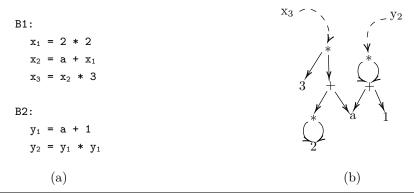

| 2.8  | Shared value graph on the right (b) with the corresponding code on the left (a), where                              |    |

|      | B1 and B2 are two different basic blocks. The shown instructions are not written in any                             |    |

|      | specific programming language                                                                                       | 12 |

| 2.9  | Simple while loop in (a) without unfolding. Loop in (a) but with ${\tt k} = 0$ unfolding in (b),                    |    |

|      | k = 1 unfolding in (c) and $k$ = 2 unfolding in (d) for bounded model checking                                      | 13 |

| 2.10 | Symbolic execution tree for the code in Fig. 2.9 (a). Only one iteration of the loop is shown,                      |    |

|      | and two cases where the condition $\mathtt{a} < 10$ is false                                                        | 16 |

| 2.11 | A fragment of code motivating <i>undef</i> from [35] in (a), a snippet of code in (b) to show how                   |    |

|      | undef could be problematic and an incorrect optimization illustrating one detail with undef                         |    |

|      | in (c)                                                                                                              | 17 |

| 2.12 | An optimization for the LLVM IR that transforms a + b > a into b > 0                                                | 18 |

| 2.13 | The GVN optimization with source (a) and target (b), loop unswitching with source (c) and target (d), and a version of loop unswitching adjusted with freeze (e) | 18  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1  | Simple loop example with A as the loop header. We have a total of four edges, from which                                                                         |     |

|      | only the edge (B,A) is a back-edge                                                                                                                               | 22  |

| 3.2  | (a) A single reducible loop with A as header. (b) Two loops, one irreducible with header A                                                                       |     |

|      | and the second reducible loop with header B. The loop is irreducible because of the edge                                                                         |     |

|      | (entry, B) which is another loop entry to the loop in addition to the loop entry $(A,B)$                                                                         | 23  |

| 3.3  | An irreducible loop $\ell_2$ with header C nested in a reducible loop $\ell_1$ with header A. $\ell_1$ is                                                        |     |

|      | reducible due to the single loop entry in A, but $\ell_2$ is irreducible because of the edges (A,C)                                                              |     |

|      | and (A,D)                                                                                                                                                        | 24  |

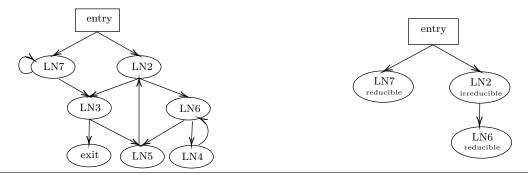

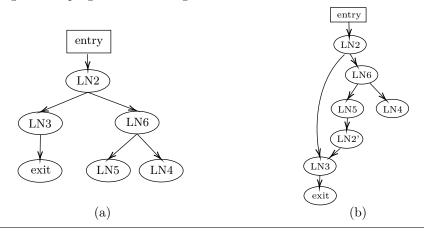

| 3.4  | Example program CFG on the left with a Loop Tree represented on the right, obtained                                                                              |     |

|      | from running the loop identification algorithm presented in [36] on the program on the left.                                                                     | 2.0 |

|      | Since we have at least one irreducible loop, the loops identified may vary                                                                                       | 26  |

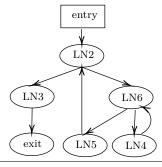

| 3.5  | A control-flow graph with two nested reducible loops.                                                                                                            | 26  |

| 3.6  | A control-flow graph with two nested reducible loops and without back edges                                                                                      | 27  |

| 3.7  | A control-flow graph with two nested reducible loops, where LN2 was duplicated                                                                                   | 27  |

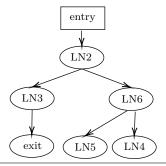

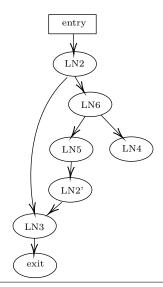

| 3.8  | A control-flow graph unrolled with a factor $k$ of 1                                                                                                             | 28  |

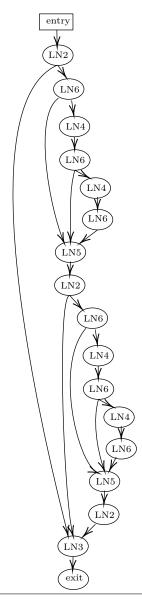

| 3.9  | A control-flow graph unrolled with a factor $k$ of 2                                                                                                             | 29  |

|      | Unroll of all loops in a program which are represented in a loop tree LT                                                                                         | 30  |

| 3.11 | Loop unroll pseudocode to unroll a single loop $L$ with an unroll factor of $k$                                                                                  | 31  |

| 3.12 | A program CFG on the left and a unrolled CFG on the right with $k=1$ respective to the                                                                           |     |

|      | CFG on the left                                                                                                                                                  | 32  |

| 3.13 | A program control flow graph (a) and its semi-unrolled control flow graph (b)                                                                                    | 32  |

| 3.14 | Loop unroll pseudocode to unroll all loops in a program and update program instructions.                                                                         | 33  |

| 3.15 | Create a phi instruction and initialize necessary data structures                                                                                                | 34  |

| 3.16 | Get the most recent duplicate of a given instruction, else return reference instruction if                                                                       |     |

|      | none found                                                                                                                                                       | 35  |

| 3.17 | Update entries of each phi instruction                                                                                                                           | 36  |

| 3.18 | Update the operands of each non-phi instruction                                                                                                                  | 36  |

| 3.19 | Remove unused phi instructions                                                                                                                                   | 36  |

| 3.20 | Duplication of a basic block and the necessary initialization of auxiliary data structures. $$ .                                                                 | 37  |

| 3.21 | Node splitting technique applied on the graph on the left results in the graph on the right.                                                                     | 39  |

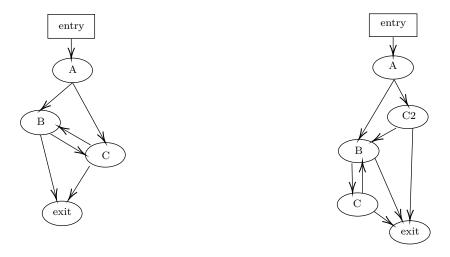

| 4.1  | Simple program with two if statements, one in A and one in C                                                                                                     | 43  |

| 4.2  | Base algorithm for constructing smaller SMT formulas in Alive                                                                                                    | 44  |

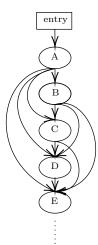

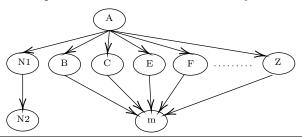

| 4.3  | A generalization of a DAG with maximal number of directed edges. Each vertex has a                                                                               |     |

|      | directed edge to all its descendants                                                                                                                             | 46  |

| 4.4  | An example program CFG to the left (reproduced from Fig $4.1$ ) with the respective                                                                              |     |

|      | dominator tree on the right, where A dominates B, C, E and F, while D is dominated by B.                                                                         | 48  |

| 4.5  | A program with an <i>if-then-else</i> statement. Vertex D has no predecessors and is designated                                                                                        |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | as a dead basic block                                                                                                                                                                  | 49 |

| 4.6  | A CFG that describes a program with an if statement without an else statement. We have                                                                                                 |    |

|      | a fork in vertex A, and a merge in C                                                                                                                                                   | 49 |

| 4.7  | Improved version of the UBReduction algorithm by making use of the post-dominance                                                                                                      |    |

|      | relation between vertices                                                                                                                                                              | 50 |

| 4.8  | Improved version of the UBReduction algorithm by making use of a conditional post-                                                                                                     |    |

|      | dominance relation between vertices                                                                                                                                                    | 51 |

| 4.9  | m does not post-dominate A because of a single path, resulting in all successors of A except                                                                                           |    |

|      | N1 to have a reference to the expressions in $m$                                                                                                                                       | 52 |

| 4.10 | $\label{thm:cond-postdom} \mbox{Heuristic based version of the UBReductionCondPostdom algorithm.} \ \ldots \ $ | 53 |

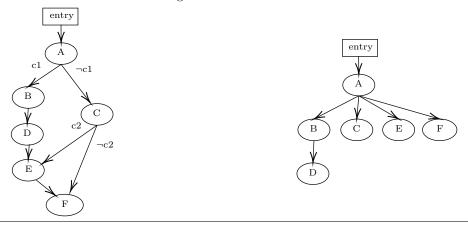

| 4.11 | A control flow graph similar to the one in Fig. 4.1, but with an additional conditional jump                                                                                           |    |

|      | in A and a merge in D                                                                                                                                                                  | 54 |

| 4.12 | SMT formula reduction algorithm for phi instructions                                                                                                                                   | 55 |

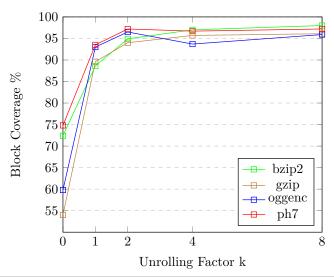

| 5.1  | Average block coverage measured after loop unroll on four different benchmarks                                                                                                         | 58 |

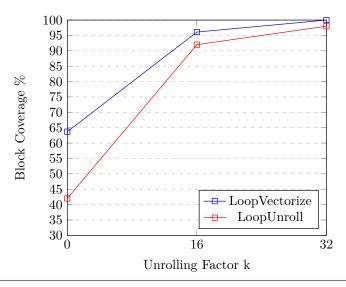

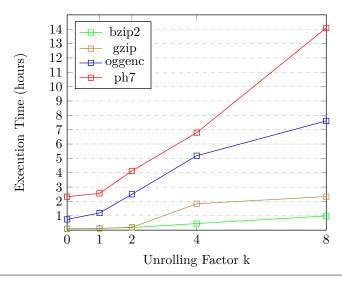

| 5.2  | Average block coverage measured for the Loop<br>Vectorize and LoopUnroll test sets                                                                                                     | 58 |

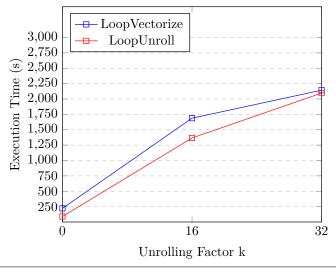

| 5.3  | Total execution time in hours of loop unroll of the four different benchmarks                                                                                                          | 59 |

| 5.4  | Total execution time in seconds through loop unroll of two LLVM test sets, namely loop                                                                                                 |    |

|      | vectorization and loop unroll                                                                                                                                                          | 59 |

| 5.5  | Example 1 of LoopReroll with the original on left and the optimized one on the right. $$ . $$                                                                                          | 61 |

| 5.6  | Example 2 of LoopReroll with the original on left and the optimized one on the right                                                                                                   | 61 |

# Chapter 1

# Introduction

It is common to have programs execute in ways that developers did not intend them to. Often, the root cause of the program misbehaving ends up being the program itself, regardless of whether the blame is put on the program or on something else entirely. In reality however, compilers are not bug-free and can miscompile more often than we would expect. For example, Fig. 1.1 shows a bug in the *instcombine* LLVM optimization pass. Here the transformation is mathematically correct when using real arithmetics, but not when using the modular arithmetics that we see in computing. In particular, b is  $x * 2^c / d$  before the transformation (source) and is  $x / (d / 2^c)$  after it (target). As a program transformation it introduces division by zero when having for instance x = 0, c = 3 and d = 7, where b = 0 / 7 in the source and b = 0 / 0 in the target.

```

int a = x << c;

int b = a / d; \Longrightarrow int t = d / (1 << c);

int b = x / t;

```

Figure 1.1: Incorrect transformation showcasing the subtleties of compiler math.

As we can see, just like almost any software, compilers are not bug-free. Compiler bugs become especially concerning when safety-critical applications are involved. Some of these bugs can be hard to find and can remain latent for a long time. Finding and resolving as many compiler bugs is thus especially important. Doing this is not trivial since compilers can be extremely large and complex to the point that verification through manual inspection becomes impractical and too difficult. Compiler correctness verification techniques such as *Translation Validation* (TV) [2] and *Compiler Verification* are helpful to resolve this issue and are in use by many different correctness verification tools [3–7]. Compiler fuzzing tools that randomly generate test cases are also interesting approaches to finding bugs. In particular, CSmith [3] is a randomized test-case generation tool and in a period of three years it was successful in finding more than 325 previously unknown bugs to compiler developers. Orion [4] created a practical implementation of *Equivalence Modulo Inputs* (EMI) for validating C compilers, and their extensive testing at the time has led to 147 confirmed bugs in GCC and LLVM. Athena [5] is also based on EMI and has found 72 new bugs in GCC.

Figure 1.2: (a) Compiler Verification: The compiler is verified prior to compilation. (b) Translation Validation when performed at each step of compilation: during compilation, the source code is transformed to an intermediate representation (IR) at each compiler step. Then the previous  $IR_i$  and the new  $IR_{i+1}$  are fed into the translation validator.

Translation validation is a simpler approach over compiler verification, where the source and the target code of some transformation are compared and checked to see whether the target is a *refinement* of the source, meaning that the target only shows behavior that we would see from executing the source program. Moreover, since program optimization usually involves multiple smaller transformations, the accuracy of translation validation can be improved by also validating each pair of different program versions constructed during compilation at the cost of more time spent in analysis.

Compiler verification on the other hand checks whether individual optimizations are correct before any program is even compiled. Compiler verification proofs are created once and remain valid for all programs compiled and optimized by the compiler for a particular optimization.

Neither approach is better than the other as both are useful and have different use cases. For instance, we would opt for translation validation when either the compiler code base is not available or too complex. Similarly, compiler verification would be the better choice when the computational cost incurred with translation validation is too high or when we want to verify a transformation as correct regardless of the input values. Fig. 1.2 illustrates the differences between compiler verification and translation validation for each optimization step.

In this thesis we extend Alive [1], a compiler verification and translation validation tool for proving LLVM optimizations as correct even when under the presence of undefined behavior. Such programs become non-deterministic and behave in unpredictable ways.

Since current Alive's translation validation tool drastically increases program compilation time, it cannot be deployed for all users. As an effort to improve Alive's performance we present algorithms to reduce the sizes of correctness proofs built by Alive resulting in a reduction of time spent checking these proofs in the Z3 [8] SMT solver, which is the dominant factor in Alive's total execution time. Specifically, we find that Alive's representations of undefined behavior and semantics of phi instructions have a lot of redundancy that can be eliminated. Phi instructions assign values to variables depending on the history of program control-flow. Although Alive uses the Z3 SMT solver, other SMT solvers such as STP [9], MathSAT5 [10], CVC4 [11] and Boolector [12] exist with varying support on different SMT theories. The

main goal of Alive is to identify as many bugs as possible in compilers such as LLVM that result in miscompilation, often with the consequence of programs misbehaving in real life situations. Ideally we would want to eliminate the chances of miscompilation, but sadly this is almost impossible to achieve. Instead, improving accuracy and coverage of Alive's program analysis is an ongoing effort.

```

int main() {

int i = 0;

while (i < 10) {

foo(i++);

}

return i;

}</pre>

```

Figure 1.3: Simple program with a while loop written in C.

In addition to performance improvements, in this thesis we want to improve how Alive handles loops. Due to limitations to the *symbolic execution* program verification technique that Alive relies on to construct proofs, Alive cannot cover the body of most program loops. Consider the example program in Fig. 1.3, because Alive currently does not cover paths that do not reach some program exit or paths that visit the same instruction twice, the call to *foo* for instance is not covered by Alive's analysis. Doing so requires Alive's symbolic execution to visit i < 10 twice and the return once.

As an additional step towards increasing the chances of finding bugs in LLVM we present a loop unrolling algorithm to solve this problem. This algorithm duplicates portions of program loops for a bounded number of times such that some loop instructions can be visited more than once in a controlled manner. This increases Alive's coverage while also avoiding limitations of *symbolic execution*. Loop unrolling can result in significant increases in program size, especially when we have deeply nested loops, therefore choosing the loop unrolling factor must be done with care.

#### 1.1 Thesis Overview

This thesis is structured into four parts. We start by giving a brief summary of related work in Chapter 2. In Chapter 3 we present solutions to improve how loops are analyzed in Alive. Specifically, we extend Alive such that it can analyze more iterations of each loop and cover more program paths and regions of code that were previously ignored.

In Chapter 4 we make use of existing graph theory concepts and develop our own control flow graph (CFG) analysis algorithms for better construction of SMT formulas in Alive, reducing their size, complexity and computational cost incurred by running an SMT solver, which is a dominant factor in the overall program analysis time. Given that our improvements to loop analysis in Alive cause programs to increase significantly in size, reducing the execution time of Alive's analysis with these algorithms should be useful in mitigating the added cost of loop unrolling.

Lastly, we discuss our results obtained from both our SMT formula reduction and loop unroll algorithms in Chapter 5 which includes performance analysis, increase in Alive's coverage and bugs found in LLVM.

# Chapter 2

# Related Work

The notion of translation validation was initially presented in the work [2], where each run of the compiler was followed by a validation phase to verify whether the target correctly implemented the source program. Many works since then have explored this technique to validate either any optimization in general [13–17], or target specific optimizations such as instruction scheduling [18], lazy code motion (LCM) [19] and software pipelining [20].

Program analysis techniques such as *symbolic execution* used in [15, 18] have proven to be quite useful in translation validation. For instance Necula [15] uses symbolic execution to compute a simulation relation between two programs. A simulation relation is a witness that describes the conditions in which two programs are equivalent. Witnesses are independent of the optimization procedure and can be produced once, and are used as proofs that some transformation is correct.

### 2.1 Compiler Verification and Translation Validation

Alive [1] is a translation validation and compiler verification tool to aid in writing correct LLVM optimizations, automatically proving them correct even in the presence of LLVM's undefined behavior. Verification consists in checking that a transformation is correct for any input, where as validation only checks a specific transformation with one combination of the inputs. Rhodium [7] is a compiler verification tool that writes automated soundness proofs with facts obtained through data-flow analysis.

As for translation validation, many different tools have been developed in previous works, including:

- Whether the tool only supports validating programs to which only one transformation was applied [19–21], or combinations of transformations [22];

- Some only validate specific optimizations [18–20] while others validate any optimization [13, 21];

- The tool uses a simulation relation [15] or a more complex representation such as a graph to reason about program equivalence [13, 17];

- Whether or not the tool takes the possibility of and the different forms of undefined behavior into account in translation validation [13, 23]. For example, if the possibility of signed integer overflow in C or C++ is considered.

```

int f(a,t) {

a = t + 1;

a = t + 2;

return 1;

}

(a)

int g(a,t) {

a = t + 3;

return 1;

}

```

Figure 2.1: An example of a transformation with the source code in (a) and the target code in (b).

**Figure 2.2:** Combined Program Expression Graph (PEG). The dashed lines represent the equality relations generated in the equality saturation technique between graph vertices, and in this case, both  $f_{\sigma}$  and  $g_{\sigma}$ , representing the heap resulting of executing a function f and g respectively, are equivalent.

Peggy [16] constructs a purely functional representation of the return values and the heaps of both the source and target programs for a given transformation. An example of a PEG is shown in Fig. 2.2, for the program code shown in Fig. 2.1. The vertices  $\mathbf{f}_{\sigma}$  and  $\mathbf{g}_{\sigma}$  correspond to the heaps of the functions  $\mathbf{f}$  and  $\mathbf{g}$  respectively. Similarly,  $\mathbf{f}_{\mathbf{v}}$  and  $\mathbf{g}_{\mathbf{v}}$  represent the return values. Since both the PEG for the source and the one for the target are used in the same PEG space, we obtain a single combined PEG, where vertices are shared when possible. After the combined PEG is constructed, the authors proceed with adding equality relations between its vertices, based on axioms created through a technique called *equality saturation*. In this example, equality saturation builds the following equality relation:

$$store(store(\sigma, a, t+1), a, t+2) = store(\sigma, a, t+3)$$

(2.1)

This relation is added into the PEG in the form of a dashed line. If the return values are equal, and if the program heaps are equivalent, then the tool developed by the authors concludes that the program transformation from f into g is correct. The equality saturation technique was developed in their previous work and can be seen in more detail in [24].

CompCert [6] takes an interesting approach by using both the compiler verification and translation validation approaches into one, where a verified translation validation algorithm is used when correctness proofs are too difficult to build with compiler verification.

CRELLVM [14] generates correctness proofs alongside translation validation. These proofs are witnesses of correctness of the compiler transformation and are independent of the optimization procedure. In this work, the witnesses are written in *extensible relational hoare logic* (ERHL) allowing them to be easily

and quickly checked with an interactive proof assistant such as Coq, reducing the need to run translation validation more than once. Similarly to these proofs constructed in CRELLVM, a simulation relation is also a witness. Instead of using ERHL, Alive encodes program semantics into the SMT (Satisfiability Modulo Theory) language, and then correct program compilation is verified by using the Z3 SMT solver with the SMT formulas Alive generates as input.

The work [20] presents a translation validation tool that addresses the *software pipelining* loop optimization. Software pipelining overlaps multiple iterations of a loop to better exploit instruction-level parallelism. The authors in this work can decompose loops into a loop prolog, a steady state and an epilogue which significantly simplifies validation for this particular optimization.

The work in [19] constructs a translation validator verified in Coq for the *lazy code motion* (LCM) optimization. LCM may also include the loop invariant code motion transformation that moves invariant instructions out of loops. To validate this transformation, their work relies on *data-flow analysis* techniques to verify that the values assigned to variables moved to different points in the target code are maintained.

Both [19] and [20] validate specific loop optimizations. In practice, the number of different compiler optimizations that can be applied is large, and having a tool that can validate any given program transformation is very useful. Currently Alive can check most program transformations, however, it currently falls short in validating loop optimizations. Loops are difficult to validate as several program analysis techniques do not work well with them. Symbolic execution is an example of such a technique. Alive uses it to encode program semantics into the SMT language before passing it into an SMT solver. The drawback with symbolic execution is that information about the program state of each loop iteration must be kept in order to represent the semantics of a given program. When a loop has a sufficiently large number of iterations, this results in an extremely large amount of memory being used. In the context of Alive, this means that the encoding of program semantics written in the SMT language just becomes too large to be verified in a realistic amount of time. In this thesis we improve upon the current implementation of Alive by unrolling program loops for a bounded number of times, improving the accuracy of Alive's translation validation tool whilst also avoiding the drawbacks of techniques like symbolic execution on loops with a high enough number of iterations.

TVOC [22] is a translation validation tool that presents a new way of modelling loops by characterizing them by key features, allowing validation of loops without needing to deal with the limitations of some program analysis techniques. These features can be for instance the number of loops, the number of instructions in each loop and the set of values that each loop index variable can take. This way of representing loops significantly simplifies loop validation as we can quickly identify which loop optimizations were applied, by observing how these key features change from source to target in a compiler transformation. To illustrate the benefits of this representation of loop structures, consider the code in Fig. 2.3, where we observe that: (i) target code (i) is one loop shorter than the source (i); (i) the target (i) has an additional instruction in the loop which corresponds to the instruction of the second loop in the source. These differences in terms of the number of loops and the number of instructions in each loop body closely resemble the loop fusion optimization, and thus validation of the transformation reduces to validating the application of this optimization. Knowing what optimization to validate and by having code specifically

Figure 2.3: A loop fusion optimization example. Source code on the left (a) and target on the right (b).

built for validating certain optimizations can significantly simplify and improve the effectiveness of the TVOC validation process. One notable difficulty in validating programs with loops is knowing which loops in the source correspond to which loops in the target. TVOC does not deal with this issue and assumes that this mapping between loops is known beforehand.

Another aspect to consider when validating loop transformations is that these are often applied in a particular order. Because TVOC already has some information on the order in which compilers usually apply certain optimizations, TVOC can confidently guess this order. Afterwards, TVOC checks each guess by constructing intermediate versions of the program through program synthesis, a technique that can be used to generate code from formal specifications. With this TVOC is then able to validate the transformation by checking each subsequent pair of generated intermediate programs. If the validator concludes each subsequent pair as equivalent then the transformation is deemed correct.

Identifying the loop transformations applied on a given program can help improve the accuracy of validation of each program transformation. This unfortunately is not as scalable because separate checks dedicated for each compiler optimization are required. Alive does not follow this approach and instead builds a more thorough representation of program semantics that is independent of the applied compiler optimizations.

The work [13] is similar to Alive, where the range of optimizations that can be validated is large and unknown to the validator. The authors in [13] focus on incrementally building a representation of the correlations between points in the source and in the target programs of a given compiler transformation. Afterwards, constraints on program values and memory states, called the predicates, are associated with each correlation. The validator then only needs to check these predicates similarly to how a simulation relation is checked in Necula [15], without any knowledge about the optimizations performed by the compiler.

In contrast to most of the related work mentioned so far, [13] also supports optimizations with some potential undefined behavior. Alive takes this a step further and fully encodes undefined behavior of programs written in LLVM IR, which greatly increases the number of miscompilations that it can find.

### 2.2 Program Representations

To properly reason about a program's structure and semantics, we need clear representations of program code. These representations can have a variable level of abstraction. Programming languages as Java and

Python are high-level languages, while LLVM IR and Alive IR are low-level program representations.

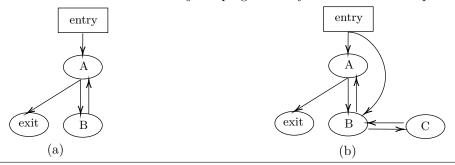

#### 2.2.1 Control Flow Graph

We define a control flow graph (CFG) as a pair (V, E), where V represents the graph vertices and E represents the directed edges between these vertices. A CFG gives a clear and visual representation of program structure and control flow. An example of a CFG is illustrated in Fig 2.4.

Figure 2.4: A control flow graph (b) for the example program (a).

#### 2.2.2 Programs in LLVM IR

Each program in LLVM IR is divided into basic blocks that represent sequences of instructions between control-flow altering instructions. For well defined programs, whenever control flow enters a basic block, all its instructions are executed. The vertices of a CFG represent basic blocks identified by some label while the edges represent the control flow of the program defined by LLVM IR instructions such as br for branches and switch for switches.

#### 2.2.3 Intermediate Representations

Both Alive IR and LLVM IR are written in a Static Single Assignment (SSA) form where each new assignment to a variable initializes a fresh variable. SSA was originally created for compilers, but turned out to also be useful for program analysis and correctness verification. Verification conditions are another use of SSA, each representing some relationship between an aspect of the source and the target program. For example, one verification condition could state that one variable in the source is equal to some variable in the target. Note that since each variable modification will result in the initialization of a new variable in SSA, the value of each variable never changes, thus the verification condition can be checked at any point in time. TVOC [22] makes use of verification conditions and aggregates them to form inductive proofs of correctness of compilation. As an example of SSA, consider the two fragments of code in Fig 2.5.

```

x = 4; x_1 = 4; y = x + 2; y_1 = x_1 + 2; x = y; x_2 = y_1;

```

Figure 2.5: Example illustrating the differences between code not SSA form on the left and the code in SSA form on the right.

With SSA we can also construct logical expressions that represent a sequence of instructions. An example of such an expression for the code fragment b) in Fig 2.5 would be:

$$x_1 = 4 \land y_1 = x_1 + 2 \land x_2 = y_1 \tag{2.2}$$

If we attempt to construct an expression from code not in SSA we would get:

$$x = 4 \land y = x + 2 \land x = y \tag{2.3}$$

Feeding the expression in Equation 2.3 into an SMT solver for proving would not work since x cannot represent two different values simultaneously. Program analysis techniques such as symbolic execution and bounded model checking make heavy use of SSA form.

In addition to SSA form, a program can also be written in *Static Single Information* (SSI) form which is an extension of SSA. SSI gives path-sensitive information in addition to flow-sensitive information with SSA by associating branch predicates with variable names at certain points in the program. SSI is useful for path-sensitive analysis techniques, an example of which is *range analysis*, a technique that maps integer variables to the possible ranges of values they can take throughout program execution. For instance, we can eliminate code that is not reachable unless a variable takes specific values. We can remove some array out of bounds checks and integer overflow detection checks, and we can improve optimizations such as constant propagation, where variables and arithmetic operations can be replaced by constants if these variables and arithmetic operands are proven to also be constant. An example of a code fragment in SSI form can be seen in Fig. 2.6.

$$y_0 = x_0 + w_0$$

if  $(y_0 < 0)$

$$y_1 = \pi(y_0)$$

$$y_2 = -y_1$$

else

$$y_3 = \pi(y_0)$$

$$y_4 = \varphi(y_2, y_3)$$

**Figure 2.6:** A code fragment in SSI form where the variables  $y_2$  and  $y_3$  are associated with the branch predicate  $y_0 < 0$  through the  $\pi$ -function.

Gated Single Assignment (GSA) is another extension of SSA that represents loops in a higher level of abstraction. GSA provides three different pseudo-functions to represent control-flow dependent values within loops. Consider the example loop in Fig. 2.7. Note also that the **br** instruction can take either one or three operands. If only one operand is given then it is an unconditional jump. Otherwise, it takes in a condition as the first operand, and moves control-flow to the basic block indicated by the second operand if the condition is true, or to the basic block indicated by the third operand if false.

Here the phi instruction and the final assignment at loop exit are replaced by calls to two new pseudo-functions,  $\mu$  and  $\eta$ . The code appears to be in SSA form, however the creation and assignment of new variables is abstracted by these two functions in GSA. The phi instruction in the SSA version selects one of the entries given to it depending on through which predecessor of loop was traversed.

```

x_0 = c

x_0 = c

loop:

loop:

x_p = phi(x_0, x_k)

x_p = \mu(x_0, x_k)

b = x_p * 2 > n + 1

b = x_p * 2 > n + 1

br b, loop1, exit

br b, loop1, exit

loop1:

x_k = x_p + 3

x_k = x_p + 3

br loop

br loop

exit:

exit:

(c)

x = x_p

x = \eta(b, x_p)

(b)

(a)

```

**Figure 2.7:** Code example not written in Gated SSA in (a), the same example but written in Gated SSA form in (b), and a shared value graph of this example in (c).

In addition to SSA, SSI, and GSA, many other intermediate representations exist for different use cases. For example, MLIR [25] is a multi-level intermediate representation highly influenced by LLVM and SIL [26] is a high-level SSA-form intermediate representation designed specifically for the Swift programming language.

Figure 2.8: Shared value graph on the right (b) with the corresponding code on the left (a), where B1 and B2 are two different basic blocks. The shown instructions are not written in any specific programming language.

The work in [17] proposes a translation validation tool that creates and evaluates value graphs, similar to the PEG's created in [16]. Value graphs can represent dependencies between variables in a program. To illustrate, consider the two sequences of instructions designated as B1 and B2 in Fig. 2.8. Consider also that we want to check whether the variable  $x_3$  is equivalent to the variable  $y_2$ . To do this, we first create a value graph for each instruction sequence, and then combine them into a single shared value graph, where any vertex that is common to both graphs is shared in the resulting graph. As an example, the vertex representing a is shared between both variables in the shared value graph.

Once the shared graph is constructed, normalization operations are performed on the graph in order to reduce it. For example, the vertex representing the multiplication 2\*2 in B1 can be replaced by a vertex representing the number 4 through constant folding. These rewrite rules are applied in sequence until they can no longer be applied, at which point we only need to check whether  $x_3$  and  $y_2$  point to the same graph vertex in order to conclude whether both variables have equivalent values. The main difference between this work and Peggy [16] lies in the fact that shared value graphs are reduced in size through rewrite rules, while PEG's are complemented with additional equivalence relations based on constructed

equality relations. Both techniques create graphical representations of dependencies between program variables, and both can be used in translation validation.

#### 2.3 Program Analysis Techniques

#### 2.3.1 Model Checking

Model Checking [27] determines whether a given program p satisfies some given property m. In Bounded Model Checking (BMC) [28], the program is designated as the model and the property m is a logical formula over the states of p. The idea of bounded model checking is to analyze all the paths with all inputs at once up to some unfolding bound k. BMC creates a single formula that represents each unfolded program for each unfolding factor and then checks whether m is not satisfied in some unfolding. If it is not satisfied, then a counter example is produced explaining why. The formula created by BMC can be for instance a SAT formula or an SMT formula. Consider the program code (a) in Fig. 2.9 and the same code but with different levels of unfolding with k = 0 in (b), k = 1 in (c) and k = 2 in (d). By unfolding

```

void foo(int a, int w) {

if (a < 10) {

a = a * 2;

w = w + 1;

assume(a >= 10);

void foo(int a, int w) {

}

while (a < 10) {

assert(a < 10);

a = a * 2;

}

w = w + 1;

(c)

}

assert(a < 10);

void foo(int a, int w) {

}

if (a < 10) {

(a)

a = a * 2;

w = w + 1;

void foo(int a, int w) {

if (a < 10) {

assume(a >= 10);

a = a * 2;

assert(a < 10);

w = w + 1;

}

assume(a >= 10);

(b)

}

assert(a < 10);

(d)

```

Figure 2.9: Simple while loop in (a) without unfolding. Loop in (a) but with k=0 unfolding in (b), k=1 unfolding in (c) and k=2 unfolding in (d) for bounded model checking.

program (a) with k=1 unfolding as shown in (c), we obtain another program where the loop body is executed only once. If we construct an SMT formula describing both the program and the negation of the property m, we can feed this formula into an SMT solver and check whether the property always holds for some unfolding factor k:

$$a_0 < 10 \land a_1 = a_0 \times 2 \land w_1 = w_0 + 1 \land a_1 \ge 10 \land a_1 \ge 10$$

(2.4)

Note the additional  $a_1 \geq 10$  that corresponds to the negation of the property m in the final assert. Since this formula is satisfiable, the property m does not hold. Similarly, for k = 0 unfolding we get:

$$a_0 \ge 10 \land a_0 \ge 10 \tag{2.5}$$

and for k = 2 unfolding:

$$a_0 < 10 \land a_1 = a_0 \times 2 \land w_1 = w_0 + 1 \land a_1 < 10 \land a_2 = a_1 \times 2 \land w_2 = w_1 + 1 \land a_2 \ge 10 \land a_2 \ge 10$$

(2.6)

Since the formulas for all three unfolding factors are satisfiable, each one has at least one example for which the property m does not hold.

One problem with BMC is choosing the bound k. There is no easy solution because we can not be sure whether there exists a loop whose execution leads to a number of iterations greater than k. For example, if we have a loop that generates random numbers and exits when a specific one is found, it is possible to set a value of k for BMC while some execution of this loop may consist of k+1 iterations. However, it is not possible to prove that some property m is satisfied for any execution of any program.

The work in [29] discusses the possibility of computing a *completeness threshold* (CT), a precomputed bound at least as high as the highest number of iterations of any loop. Unfortunately computing the CT is as hard as model checking.

CBMC [30] is an implementation of BMC for C and C++ programs. Some applications of CBMC include verification of ANSI-C embedded software [29] and program equivalence checking [31]. In [31], an ANSI-C program is transformed into a bit-vector logic equation consisting of only nested if instructions, assignments, assertions and branch targets. The program is then further transformed into two bit-vector equations, one forming the set of constraints and the other representing the properties to check. Finally, the resulting bit-vectors are translated into *Conjunctive Normal Form* (CNF) and fed into a SAT solver to test for satisfiability. In summary, the equivalence problem is reduced into a bit-vector logic decision problem and then tested for satisfiability with a SAT solver. Similarly, CBMC also constructs a formula  $p \land \neg m$  and feeds it into a SAT solver.

#### 2.3.2 Symbolic Execution

Symbolic execution (SE) [32] is a widely used program analysis technique used to test whether certain properties are violated in a program. In symbolic execution, each input variable is associated with a symbolic variable. Moreover, an execution engine steps through the program from instruction to instruction and builds a SAT formula as a conjunction of path constraints. An example of a path constraint could be the condition of an if statement. If the symbolic engine reaches a branch statement, the symbolic execution state is forked, creating a new state for each of the branch possibilities. Each new state will possess a new set of path constraints  $\pi$  and a new symbolic store  $\sigma$ , which is a mapping between variables and values or

symbolic expressions. In particular, if a branch condition a=4 is satisfied, the a=4 constraint is added to the path constraints  $\pi_{\text{true}}$  of one child of SE, while  $a\neq 4$  is added to the path constraints of  $\pi_{\text{false}}$  of the other child. In the case that the execution engine encounters an assignment, the respective mapping for the assigned variable in the symbolic store  $\sigma$  is updated. Additionally, in symbolic execution a model checker can eventually be used to test whether the constraints of a given path are violated. If the model checker finds that the path constraints have been violated, the respective path is pruned, as the path will always be infeasible despite any new constraints that could be added to its path constraints  $\pi$ .

In summary, symbolic execution will simulate an increasing number of program paths simultaneously as new branches are encountered, thus SE is an incremental program analysis technique. This of course leads to a big problem when loops are involved, namely *state space explosion*. For each iteration of a loop the symbolic execution state can be forked more than once and lead to even more states with their own path constraints and symbolic stores. For this reason, maintaining an increasing number of different symbolic stores can incur in a heavy memory cost.

Besides state space explosion and memory concerns, symbolic execution also does not deal well with calls to libraries or system code. Some variations of symbolic execution can mock or ignore calls to code outside the program, but this affects the effectiveness of this technique. Moreover, the model checker that is usually based on *satisfiability modulo theory* (SMT) solvers will eventually test whether any constraints of a path have been violated, which can become quite a burden on the constraint solver when the path constraints become too much to handle.

The survey [33] discusses numerous different techniques towards mitigating the main challenges of symbolic execution. For instance, selective symbolic execution (S<sup>2</sup>E) [34] is a technique where some paths of the software stack can be explored concretely. Instead of symbolic variables, program variables are associated with specific values similarly to normal program execution. With S<sup>2</sup>E, the calls to system code and libraries can be executed concretely, which is a lot faster than doing it symbolically as the path to be taken is pre-defined implicitly by the concrete values assigned to the program variables during execution.

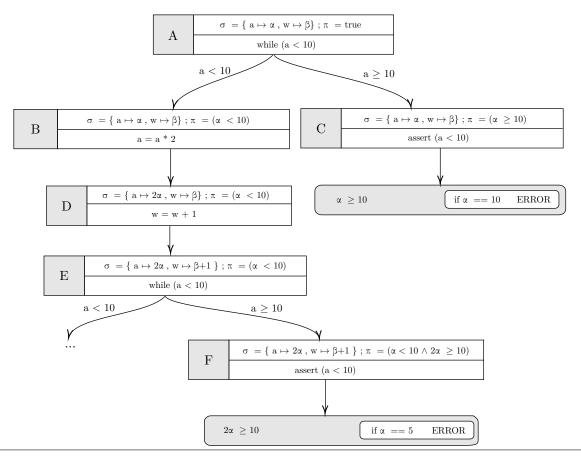

To better illustrate how symbolic execution works, Fig. 2.10 shows the symbolic execution tree for the program with the simple while loop seen previously in Fig. 2.9 (a). Each labeled box represents the state of the symbolic execution engine, each having one symbolic store  $\sigma$ , a set of path constraints  $\pi$ , and the next statement to execute. In state A, the engine encounters a while loop and the execution state is forked. The child that explores the new state with the path constraint  $\alpha \geq 10$  brings the engine to an assert statement assert (a < 10) which tests a property m. Here the model checker tests whether m is violated in this path by checking the formula  $\alpha \geq 10$  with for example an SMT solver. Note that a corresponds to the value of a when testing the loop condition in state A. In this path the formula is satisfiable, proven by showing the example  $\alpha = 10$ . As a consequence, the property m is violated at least once and the engine has found an error state. Similarly, if the path to B and then to F is tested first, we reach the assert statement with another error state. To see why, consider an example where we have  $\alpha = 5$ , with  $\alpha$  corresponding to a having value 5 at state A, and  $\alpha = 10$  after the first loop iteration, then  $\alpha \geq 10$  is satisfiable.

Figure 2.10: Symbolic execution tree for the code in Fig. 2.9 (a). Only one iteration of the loop is shown, and two cases where the condition a < 10 is false.

#### 2.3.3 Bounded Model Checking vs. Symbolic Execution

Both techniques can be used to check whether a property holds for a given program. The primary differences between bounded model checking and symbolic execution are: (i) BMC runs a single SAT formula in order to search for a counter example in executions of the loop unrolled program with an unrolling factor k. However, symbolic execution runs SMT queries in parallel, running new ones whenever the symbolic execution engine encounters a branch; (ii) BMC is bounded by an integer k while symbolic execution will keep running until all feasible paths have been explored; (iii) symbolic execution prunes paths that its model checker found infeasible while BMC is forced to keep searching; (iv) symbolic execution runs on symbolic inputs as opposed to BMC running with concrete inputs.

Because symbolic execution runs SMT queries in parallel and can prune infeasible paths early, symbolic execution is a more suitable choice towards analyzing programs with a higher number of paths as these paths are more likely to share unsatisfiable SMT prefixes.

Since BMC uses concrete values while symbolic execution uses symbolic variables, symbolic execution is more appropriate towards analyzing programs with undefined behavior, because BMC would be forced to test for every possible value as some operations can return any arbitrary value of a given type. In particular, a variable in LLVM IR may be marked as *undef*, a form of deferred undefined behavior that when read, is allowed to return any value within the range of values that the variable's type can represent.

#### 2.4 Undefined Behavior

If a program produces different results at least once with the same inputs, then the program is non-deterministic. In order to correctly validate a program transformation with translation validation we need to also understand what the sources of non-determinism are and how they work. One type of non-deterministic program behavior is undefined behavior.

Undefined behavior can be classified into three types, (i) immediate undefined behavior leads to any kind of result when executed; (ii) undef returns an arbitrary value of a given type when read; (iii) poison is a stronger variant of undef as it also taints the control flow graph by propagating poison to subsequent instructions. In contrast to immediate UB, undef and poison are deferred, meaning that they do not immediately lead to the execution of UB. Deferred undefined behavior is useful as it allows for some optimizations such as speculative execution to exist. To illustrate the motivation for undef consider the code (a) in Fig 2.11.

```

int x;

if (cond) {

x = f();

}

if (t != 0) {

a = 1 / t;

}

if (cond2) {

g(x);

}

(b)

y = 2 * x; ⇒ y = x + x;

}

(a)

```

**Figure 2.11:** A fragment of code motivating *undef* from [35] in (a), a snippet of code in (b) to show how *undef* could be problematic and an incorrect optimization illustrating one detail with undef in (c).

If the condition cond is false and cond2 is true, then x is used before it is initialized. In particular for LLVM, an extra instruction is produced for every variable that is used before it is initialized. This can incur quite a performance cost in the long run. Instead, LLVM compiles it such that the uninitialized variables return undef when used, thereby not adding extra instructions and as a consequence avoiding the performance cost.

Undef is not a perfect solution. Consider the code (b) in Fig. 2.11. If t is undef, then every read to t returns an arbitrary value of its type. Therefore, it is possible that on the first read of t returns a value different than zero, and the second read returns zero. In that case, the code (b) in Fig. 2.11 will lead to division-by-zero which is immediate undefined behavior when executed. Moreover, duplicating usages of undef can be dangerous, consider code in (c) in Fig. 2.11 and assume that x and y are 1 byte-sized unsigned integers. If x is undef, then  $x \in [0, 255]$  and thus the possible values of y would be any even number within [0, 254]. However, if we apply the optimization, the possible values of y = x + x would be in [0, 255] as x can be read once as odd and once as even. Therefore, y after the optimization can have odd values but not before, thus the transformation is incorrect.

To see why poison is necessary, consider the LLVM IR optimization in Fig. 2.12. If a is INT\_MAX and b is 1, we get INT\_MAX + 1 > INT\_MAX, which simplifies to undef > INT\_MAX because INT\_MAX + 1 is signed integer overflow and considered undefined. This transformation is incorrect as no value of a given

Figure 2.12: An optimization for the LLVM IR that transforms a + b > a into b > 0.

```

while (c) {

t = x + 1;

if (t == y) {

if (c2) { foo(); }

w = x + 1;

else { bar(); }

foo(w);

}

if (freeze(c2)) {

}

while (c) { foo(); }

(c)

else {

(a)

while (c) { bar(); }

if (c2) {

t = x + 1;

while (c) { foo(); }

if (t == y) {

} else {

(e)

while (c) { bar(); }

foo(y);

(d)

(b)

```

Figure 2.13: The GVN optimization with source (a) and target (b), loop unswitching with source (c) and target (d), and a version of loop unswitching adjusted with freeze (e).

type can be greater than the highest value the type can represent. On the other hand if we do apply the optimization we get b > 0 which simplifies to 1 > 0 which of course is true. In summary, we are getting different results before and after the optimization and thus this transformation is incorrect. To go around this problem, in the particular case for LLVM IR, the nsw attribute ("no signed wrap") is added to the add instruction in this optimization, which makes the instruction instead return poison on overflow. This allows us to still take advantage of the optimization by deferring the undefined behavior as poison, which can then be propagated to subsequent instructions.

The work [35] proposed a new 'freeze' instruction, now present in the LLVM IR. Freeze is an instruction that either returns an arbitrary value for a given type if the input is poison, or acts as a no-op. To illustrate the authors' motivation for the freeze instruction, consider the code examples in Fig. 2.13. Assuming that (i) c is false; (ii) c2 is poison; (iii) branch-on-poison semantics is immediate UB, then for the loop unswitching transformation in (c), we do not branch on c2 because c is false, therefore immediate UB does not occur. In (d) however, because c2 is poison and since we branch on c2, we get immediate UB, therefore the target has different behavior than the source and the transformation is incorrect.

A similar case occurs in the *global value numbering* (GVN) transformation with source (a) and target (b). GVN finds expressions that are equivalent and substitutes them with one of the expressions designated as a representative, in this way removing redundant computations. Assuming branch-on-poison is not immediate UB, and y is poison whilst w is not, then the function foo is called with a poison argument in (b), but not in (a).

Since GVN and loop unswitching have conflicting branch-on-poison semantics, it would not be possible to apply both on the same code, unless the loop unswitching transformation wraps the outer if statement

condition with the new freeze instruction, as shown in (e).

The work [23] presents a way to find and model undefined behavior as invariants, either obtained through a best-effort static analysis or deeper alias analysis when more complex code with memory accesses is involved. One assumption that some compilers take during compilation is the *out-of-bounds variable access* (OBVA) assumption. OBVA states that a program will not access a memory location beyond the region allocated to an object. Consider for instance a program that is vulnerable to array buffer overflow and the compiler applies the register allocation optimization. The register allocation optimization maximizes the use of registers by allocating local variables into registers instead of memory locations in the stack. If the OBVA assumption was not taken by the compiler, then there would be a difference in semantics between the source and the target, as buffer overflow can occur with contiguous memory locations in the stack (source), but not with registers (target). This way the authors soften the equality constraints to tune the translation validation process in accordance with the assumptions that compilers make during compilation.

### 2.5 Summary

In this chapter we have given an overview on different program verification techniques such as *compiler* verification and translation validation. We reviewed some program analysis techniques such as alias analysis, symbolic execution and bounded model checking. Each technique has its own merits and use cases, and all are widely used by many developed program verification tools today.

In addition to visiting different intermediate program representations, we have given an overview on program undefined behavior and how tricky it can make the process of verifying the correctness of compiler transformations.

# Chapter 3

# Loops

Loops allow the execution of the same sequence of code repeatedly and are common in programs in general. Alive has to be able to analyze them efficiently, however doing so is not an easy task, especially given the limitations of some program analysis techniques such as symbolic execution. As was discussed previously, symbolic execution with loops can result in the traversal of a very large number of blocks, leading to memory usage problems.

Because of these limitations, Alive currently only traverses each vertex in the loop at most once by analyzing a *directed acyclic graph* (DAG) version of the original program. A DAG is a graph without any cycles and with no back edges. As a consequence of ignoring back edges, Alive can miss some vertices or paths in its analysis of programs if a program exit is not reachable from these vertices in the DAG.

**Definition 1.** A vertex v is reachable from vertex u if there exists a path starting from u that traverses v.

**Definition 2.** For a given topological ordering of vertices in V, an edge  $(u, v) \in E$  is a back-edge if the topological order of vertex v is lower than or equal to the topological order of vertex v.

**Definition 3.** For a given topological ordering of vertices in V, an edge  $(u, v) \in E$  is a forward-edge if vertex v has a greater topological order than u.

Consider the simple example in Fig. 3.1, the path  $entry \to A \to exit$  will be covered by Alive, however, the path  $entry \to A \to B \to A \to exit$  will not as the edge  $B \to A$  is replaced before symbolic execution. Later we will present an algorithm that will be capable of unrolling the program before Alive's symbolic execution, by duplicating vertices in a certain order, and consequently increasing both the block coverage and path coverage of Alive's analysis, two of the most important metrics by which our unrolling algorithm will be evaluated.

**Definition 4.** We say that a basic block b in some program p is covered by Alive if it is traversed by some covered path. A path is covered by Alive if it starts from program entry and reaches some program exit without traversing any back edges.

**Figure 3.1:** Simple loop example with A as the loop header. We have a total of four edges, from which only the edge (B,A) is a back-edge.

**Definition 5.** We define *block coverage* as the percentage of the total number of different basic blocks of a program p that are covered by Alive. Any duplicate d of some basic block b where d is inserted during loop unroll is considered the same block as b.

**Definition 6.** We define  $path\ coverage$  as the number of different paths of a program p covered by Alive.

We have total block coverage if every different basic block in a program p is covered by Alive. Total block coverage is not always possible, for instance if a program contains a basic block b with the unreachable LLVM IR instruction, and thus any path that traverses b will not reach a program exit.

Total path coverage is only possible to obtain for a program p if one of the following two conditions are met: (i) p has no loops or (ii) every loop in p does not run for some number of iterations that is greater than the unrolling factor k given to the loop unrolling algorithm, resulting in total path coverage only for the unrolled program p.

The loop unrolling algorithm that we will present in Section 3.5 adds basic blocks without the guarantee that these will be covered by Alive. To evaluate whether loop unroll improved program coverage of Alive's analysis, metrics such as *block coverage* and *path coverage* are useful.

Before we can move on to providing solutions, we must first define what a loop is and what it consists of. We begin by defining a loop as a triple  $\ell = (h, B, X)$ , consisting of a single loop header h, the loop body B and the loop exiting blocks X, which are included in the loop body B.

**Definition 7.** The loop header h of a loop  $\ell = (h, B, X)$  in a program p with the CFG = (V, E) is the loop entry vertex of  $\ell$  such that:

$$\exists u, v, w \in V : u \notin \{h\} \cup B \land v, w \in \{h\} \cup B \land u, v \in E^{-1}[h] \land w \in E[h]$$

(3.1)

The loop header h must have at least two incoming edges from two different sources, one from within the loop and another from a vertex outside the loop. Moreover, it must also have at least one outgoing edge directed at a vertex within the loop. Note also that h is not always also a loop exiting block, it is possible to have multiple loop exiting blocks without any of them being the loop header.

**Definition 8.** The loop exiting blocks  $e \in X$  of a loop  $\ell = (h, B, X)$  satisfy:

$$\exists \ u \in E[e] : \ u \notin \{h\} \cup B \tag{3.2}$$

**Definition 9.** Any successor of a loop exiting block not in the loop is called a loop exit block.

**Definition 10.** A loop  $\ell$  is *reducible* if it has exactly one loop entry.

**Definition 11.** A loop  $\ell$  is *irreducible* if it has more than one loop entry.

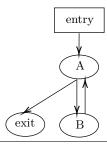

To better understand the difference between reducible and irreducible loops, consider the two CFG's in Fig. 3.2. Note that the basic block *entry* is a program entry block and not a loop entry block.

**Figure 3.2:** (a) A single reducible loop with A as header. (b) Two loops, one irreducible with header A and the second reducible loop with header B. The loop is irreducible because of the edge (entry, B) which is another loop entry to the loop in addition to the loop entry (A, B).